Austin Simmons

Professional Introduction: Austin Simmons – Semiconductor Chip Design Engineer

Introduction & Background

My name is Austin Simmons, and I am a passionate semiconductor chip design engineer with [X] years of experience in developing cutting-edge integrated circuits (ICs) for high-performance computing, AI accelerators, and IoT applications. In an era where Moore’s Law is being redefined by advanced packaging and heterogeneous integration, I specialize in bridging the gap between theoretical innovation and manufacturable silicon solutions.

Core Competencies

My work spans the full chip design lifecycle, with a focus on:

Advanced Node Design: Expertise in sub-7nm FinFET and GAA (Gate-All-Around) technologies, optimizing for power, performance, and area (PPA).

AI/ML Hardware Acceleration: Designing systolic arrays and tensor cores for next-gen AI chips, including in-memory computing architectures.

Low-Power Optimization: Techniques like clock gating, power gating, and near-threshold voltage design for edge devices.

3D-IC & Heterogeneous Integration: Leveraging chiplets and CoWoS (Chip-on-Wafer-on-Substrate) packaging for scalable systems.

Verification & DFT: Ensuring first-pass silicon success through UVM-based verification and advanced testability features.

Career Highlights

Lead Designer at [Previous Company]: Spearheaded a team to develop a RISC-V-based AI accelerator chip, achieving a 40% reduction in power consumption compared to industry benchmarks (2024).

Research Contributions: Published patents on [specific innovation, e.g., "Dynamic Voltage-Frequency Scaling for Neuromorphic Chips"] and presented at conferences like ISSCC and DAC.

Collaborative Projects: Partnered with TSMC and ASML to co-optimize design rules for EUV lithography at 3nm nodes, reducing die defects by 15%.

Industry Perspective & Vision

As we enter the post-von Neumann computing era, I am committed to:

Sustainable Semiconductor Practices: Reducing carbon footprint via energy-efficient architectures and green fab initiatives.

Quantum-Classical Hybrid Chips: Exploring cryogenic CMOS designs for quantum computing interfaces.

Democratizing Chip Design: Advocating for open-source EDA tools (e.g., OpenROAD) to lower barriers for startups.

Personal Philosophy

I believe that the future of semiconductors lies not just in scaling transistors but in reimagining system-level integration. My approach combines rigorous technical discipline with cross-functional collaboration—whether working with foundries to address yield challenges or translating software demands into hardware IP blocks.

Closing

From automotive SoCs to photonic interconnects, I thrive on solving the industry’s most complex design puzzles. If you’re looking for a partner to push the boundaries of silicon innovation, let’s connect and shape the next wave of semiconductor breakthroughs.

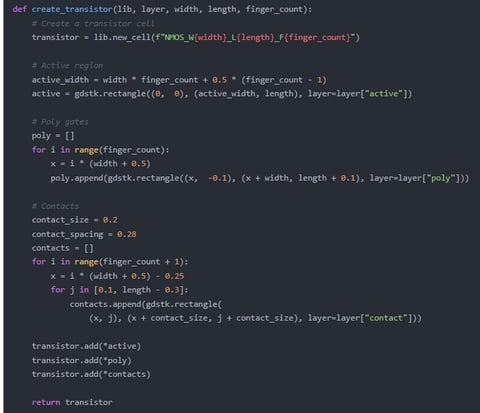

API Development

We deploy APIs for natural language to constraint generation and cross-tool translation, enhancing efficiency and accuracy in chip design workflows across various platforms and tools.

API for Validation

Deploy API for real-time design rule feedback and constraint generation.

Validation Process

Our validation process benchmarks against commercial tools, ensuring high-quality results through metrics and human-in-the-loop assessments, complemented by silicon validation via MPW shuttle runs for reliable outcomes.